Kas yra FPGA?

Integrinis grandynas, vadinamas programuojamų vartų masyvu (FPGA), susideda iš vidinių techninės įrangos blokų su vartotojo programuojamais tarpusavio ryšiais, kad būtų galima pritaikyti veikimą konkrečiam tikslui. Jungtys yra lengvai perprogramuojamos, todėl FPGA gali būti pritaikyta naujai paskirčiai arba priimti dizaino pakeitimus per visą detalės gyvavimo laiką.

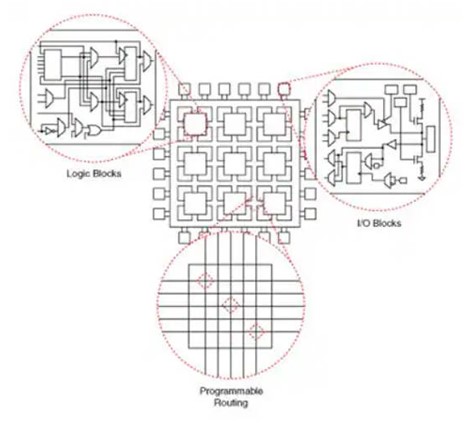

Lyginant su ASIC technologijomis su fiksuotomis funkcijomis, pavyzdžiui, įprastinėmis ląstelėmis, FPGA gali turėti įvairių privalumų. ASIC paprastai sukuriamos per kelis mėnesius, o prietaiso įsigijimas kainuoja tūkstančius dolerių. Tačiau FPGA gali būti pagaminti greičiau nei per sekundę ir gali kainuoti nuo kelių dolerių iki kelių tūkstančių. FPGA lankstumas turi didelę kainą, susijusią su vieta, galia ir vėlavimu. FPGA užima nuo 20 iki 35 kartų daugiau vietos nei įprastinis ASIC elementas, o jos sparta yra 3-4 kartus mažesnė. Šiame straipsnyje aptariami FPGA pagrindai ir FPGA architektūros modulio komutacinė matrica, loginiai blokai ir įvesties / išvesties blokas. Jei norite sužinoti daugiau informacijos apie FPGA serijas, tokias kaip „Zynq-7000 SoC“, FPGA „Spartan-7“ arba „Virtex-7“ FPGA, galite apsilankyti „Vemeko FPGA“ svetainėje ir sužinoti apie jas išsamesnės informacijos.

FPGA architektūra

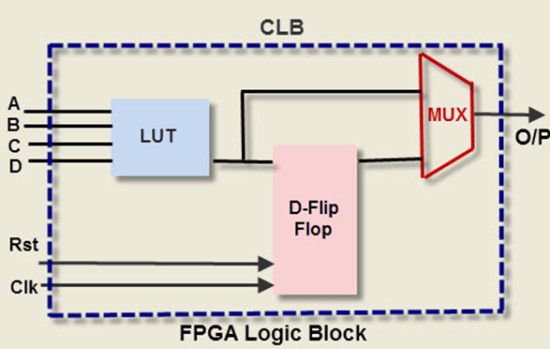

Priklausomai nuo gamintojo, CLB gali būti vadinamas loginiu bloku (LB), loginiu elementu (LE) arba logine ląstele (LC). Loginio bloko komponentai MUX (multiplekseris), D flip-flopas ir LUT. MUX naudojamas pasirinkimo logikai, LUT atlieka kombinacines logines operacijas, o D flip flopas saugo LUT išėjimą. Funkcijų generatorius, pagrįstas paieškos lentele, yra pagrindinis FPGA komponentas. Po bandymų LUT gali turėti 3, 4, 6 ar net 8 įėjimus. Dabar turime adaptyviąsias LUT, kurios naudoja du funkcijų generatorius, kad įgyvendintų du išėjimus iš vienos LUT.

Geriausiai žinomoje FPGA, „Xilinx Virtex-5“, yra flip-flopas ir paieškos lentelė (LUT), sujungti MUX. Šiuolaikinę FPGA sudaro tūkstančiai ar šimtai pritaikomų loginių blokų. Programinė įranga „Modelsim“ ir „Xilinx ISE“ naudojama kuriant ir kuriant bitų srauto failą FPGA nustatymui.

CPLD ir FPGA

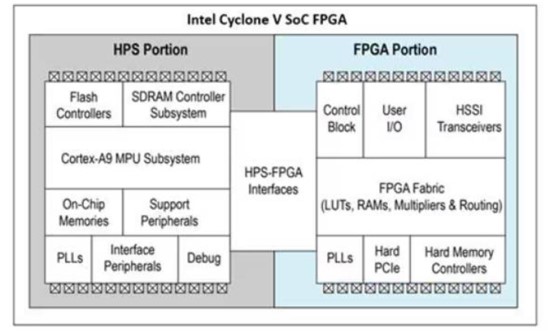

Mažos energijos sąnaudos, mažas loginis tankis ir minimalus lusto sudėtingumas – tai pagrindinės pradinio lygio FPGA savybės. Funkciniai blokai su specializuotomis funkcijomis pridedami prie aukštesnio funkcionalumo įrenginių: Keletas pavyzdžių: fazių blokuotės (PLL), didelės spartos serializatoriai ir deserializatoriai, Ethernet MAC, PCI express valdikliai ir didelės spartos siųstuvai. Šie blokai gali būti kuriami kaip nepriklausomos grandinės, t. y. kietasis IP, arba įgyvendinami su CLB, kuris vadinamas minkštuoju IP. Naudojant kietosios IP blokus našumas padidėja perkonfigūravimo galimybių sąskaita. Aukščiausios klasės FPGA produktų šeima apima sudėtingus „sistema luste“ (SoC) komponentus, kuriuose į vieną įrenginį sujungtas mikroprocesoriaus procesoriaus branduolys, kietoji IP ir FPGA architektūra. SoC FPGA užtikrina didesnę integraciją, mažesnį energijos suvartojimą, mažesnį ploto užimamą plotą plokštėje ir didesnio pralaidumo ryšį tarp branduolio ir papildomų blokų, palyginti su atskirais įrenginiais. CPLD ir FPGA pirmiausia skiriasi tuo, kad CPLD veikdami nekeičia savo konfigūracijos. Priešingai nei FPGA, kuriuos galima išplėsti ar modifikuoti veikimo metu, jų funkcijos laikui bėgant yra pastovios. Pagrindinė CPLD idėja yra ta, kad visos loginės operacijos įgyvendinamos loginiuose vartuose.

| FPGA | CPLD |

|---|---|

| FPGA naudoja daugiau energijos. | Priešingai, CPLD suvartoja mažiau energijos. |

| Sudėtingos programos puikiai tinka FPGA. | Priešingai, paprastesnės programos geriau veikia su CPLD. |

| FPGA galima rasti iki 100 000 mažyčių loginių blokų. | Palyginimui, CPLD gali talpinti tik kelis tūkstančius loginių blokų. |

| Kita vertus, FPGA yra integrinis grandynas, kuris visų pirma skirtas tam, kad klientas arba kūrėjas galėtų jį keisti po pagaminimo. | Integrinis grandynas, vadinamas CPLD, padeda veikti skaitmeninėms sistemoms. |

| Palyginti su FPGA, CPLD vėlavimai yra daug labiau nuspėjami. | Kadangi CPLD turi nepastoviąją atmintį, jam suteikiama didesnė apsauga nei FPGA. |

| FPGA priklauso smulkiagrūdžių įrenginių kategorijai. | Kita vertus, CPLD yra stambiagrūdis. |

| FPGA yra panaši į vartų masyvą. | Tačiau CPLD yra lygiavertis PAL. |

| Našumo požiūriu FPGA užtikrina patikimą našumą, kuriam neturi įtakos vidinis maršrutizavimas. | Kita vertus, CPLD našumas yra nepastovus ir priklauso nuo maršruto parinkimo. |

| Tuo tarpu FPGA yra lauko programuojamų vartų matricų (Field Programmable Gate Arrays) santrumpa. | CPLD yra sudėtingų programuojamų loginių įrenginių santrumpa. |

| Skaitmeninis loginis lustas, vadinamas FPGA, yra pagrįstas operatyviąja atmintimi. | Kita vertus, CPLD yra pagrįsti EEPROM. |

SoC FPGA apžvalga

Kad būtų galima pritaikyti įvairioms taikomosioms programoms, SoC FPGA siūlo platų apdorojimo galimybių spektrą. Didelės apimties taikomosioms programoms, įskaitant protokolų jungtis, vaizdo apdorojimo korteles, mobiliuosius įrenginius ir pramonines variklių valdymo pavaras, daugiausia dėmesio skiriama nebrangiems ir mažos galios SoC FPGA, tokiems kaip „Intel“ „Cyclone V“. Įrenginio FPGA dalis ir kietojo procesoriaus sistema (HPS), sukurta aplink vieno arba dviejų branduolių 32 bitų „Arm Cortex-A9 MPCORE“, veikiantį 925 MHz dažniu, sudaro du atskirus jo komponentus. Kiekvienas komponentas turi unikalų periferinių įrenginių rinkinį, įskaitant išorinių tiekėjų kietąjį IP.

FPGA projektavimas

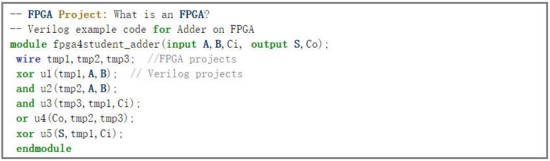

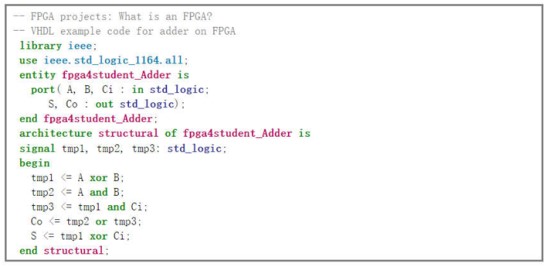

Kaip sukurti tinkamą konfigūraciją, kad būtų galima paleisti programą naudojant tūkstančius aparatūros blokų? Norint sukurti FPGA pagrįstą dizainą, reikiamas skaičiavimo užduotis pirmiausia apibrėžti kūrimo įrankyje, o tada sujungti į konfigūracijos failą, kuriame nurodoma, kaip sujungti CLB ir kitus modulius. Ši procedūra primena programinės įrangos kūrimo ciklą, tačiau vietoj to, kad būtų kuriamas instrukcijų rinkinys, skirtas veikti iš anksto nustatytoje aparatinės įrangos platformoje, siekiama sukonstruoti pačią aparatinę įrangą. Norėdami sukurti FPGA sąranką, konstruktoriai istoriškai naudojo aparatinės įrangos aprašymo kalbą (HDL), pavyzdžiui, VHDL arba Verilog.

Tai, kad projektuojant FPGA reikia ir kodavimo įgūdžių, ir nuodugnaus techninės įrangos supratimo, yra kliūtis taikant HDL metodą, nes būtinos žinios nėra lengvai prieinamos.

Pardavėjai dabar teikia programinės įrangos kūrimo rinkinius (SDK), kurie leidžia projektuotojams kurti FPGA sprendimus tokiomis populiariomis aukšto lygio kalbomis kaip C/C++, Python ir OpenCL. Taip pat yra aukšto lygio sintezės (HLS) projektavimo priemonių, kuriose naudojamos grafinės blokų diagramos, o ne kodo eilutės, ir kurios veikia tokiose platformose kaip „National Instruments“ „LabVIEW.“

FPGA programos

Galimybė konfigūruoti FPGA CLB į šimtus ar tūkstančius vienodų apdorojimo blokų taikoma vaizdų apdorojimo, dirbtinio intelekto (DI), duomenų centrų aparatinės įrangos greitintuvų, įmonių tinklų ir automobilių pažangiųjų vairuotojo pagalbos sistemų (ADAS) srityse. Daugelyje taikomųjų programų lygiagrečiai vykdomos identiškos operacijos. Daugelyje šių taikomųjų sričių vyksta sparčios permainos, nes diegiami nauji protokolai ir standartai ir keičiasi poreikiai. FPGA dėka gamintojai gali įdiegti sistemas, kurias prireikus galima keisti.

Didelės spartos paieška yra puikus FPGA panaudojimo būdas: „Microsoft“ naudoja FPGA savo duomenų centruose, kad galėtų naudoti „Bing“ paieškos sistemas. Nauji algoritmai gali būti palaikomi, nes juos kuriant FPGA atliekami pakeitimai. Pasikeitus reikalavimams, konstrukciją galima pritaikyti modeliavimo ar modeliavimo procedūroms vykdyti HPC programoje. Su ASIC tokį lankstumą pasiekti sunku arba neįmanoma. Kitos FPGA taikymo sritys – bevielis ryšys, medicininė elektronika, buitinė elektronika, skaitmeninė televizija, pramoninis variklių valdymas, kosmoso ir gynybos pramonė.

Elektronika.lt pastaba: tekstas pateiktas reklamos užsakovo.

Integrinis grandynas, vadinamas programuojamų vartų masyvu (FPGA), susideda iš vidinių techninės įrangos blokų su vartotojo programuojamais tarpusavio ryšiais, kad būtų galima pritaikyti veikimą konkrečiam tikslui. Jungtys yra lengvai perprogramuojamos, todėl FPGA gali būti pritaikyta naujai paskirčiai arba priimti dizaino pakeitimus per visą detalės gyvavimo laiką.

Integrinis grandynas, vadinamas programuojamų vartų masyvu (FPGA), susideda iš vidinių techninės įrangos blokų su vartotojo programuojamais tarpusavio ryšiais, kad būtų galima pritaikyti veikimą konkrečiam tikslui. Jungtys yra lengvai perprogramuojamos, todėl FPGA gali būti pritaikyta naujai paskirčiai arba priimti dizaino pakeitimus per visą detalės gyvavimo laiką.