Dauguma radijo mėgėjų, bandžiusių pagaminti siųstuvą, susiduria su nemažomis problemomis: generatoriaus dažnio stabilumu bei pakankama deviacija (dažninės moduliacijos atveju). Šios problemos visiškai išnyksta, pritaikius dažnio sintezatorius (DS), kurie plačiai naudojami ryšio sistemose. DS paprastai sudaro viena mikroschema, kurioje realizuotas spartus SAK (Skaičius-analogas keitiklis). Demonstracijai panaudosime pakankamai paprastą ir lengvai valdomą „Analog Devices“ sintezatorių AD9851, kuriuo tiesiogiai galima generuoti 70 MHz sinusinį signalą. AD9851 turi 32 bitų dažnio keitimo registrą, sudarytą iš atskirų 8 bitų dalių, kurios užpildomos per duomenų šyną (1 pav.). Pastarasis sintezatorius gali dirbti iki 180 MHz taktiniu dažniu (9 išvadas 1 pav.), kuris gali būti gautas iš vieno tranzistoriaus kvarcinio generatorius. Sintezatorius viduje turi dažnio daugiklį, kurį aktyvavus pasiekiamas reikiamas dažnis, naudojant mažesnio dažnio generatorius.

AD9851 sintezatorius gali būti naudojamas netiesiogiai generuoti virpesius iki 500 MHz, kadangi generuojamas sinusinis virpesys turi aukštesnes harmonikas (2 pav.). Tarkim vidinis taktinis sintezatoriaus dažnis yra 180 MHz ir generuojame 10 MHz virpesį. Tada dėl SAK atsiras papildomos harmonikos: 180 MHz - 10 MHz = 170 MHz, 180 MHz + 10 MHz = 180 MHz, 2x180 MHz - 10 MHz = 350MHz, 2x180 MHz +10 MHz = 370 MHz ir t. t. kuo aukštesnės eilės harmonika, tuo mažesnę amplitudę ji turi. Pritaikius, tarkim, 350 MHz juostinį filtrą bei galios stiprintuvą, galime gauti neblogą 350 MHz siųstuvą, kurio dažnio stabilumas tiesiogiai priklauso nuo kvarco dažnio.

2 pav. Aukštesnių harmonikų išsidėstymas 10 MHz virpesio generavimo atveju

Pastarasis dažnio sintezatorius, bandymams buvo prijungtas prie AVR mikrovaldiklio „Atmega16“. Vietoj kurio galima naudoti bet kokio tipo mikrovaldiklius, ar net tiesiogiai jungti prie kompiuterio LPT jungties (nuoseklaus jungimo režime). AD9851 mikroschema turi 40 bitų ilgio registrą, kuris suskaidytas 8 bitų skiltis. Iš viso yra 5 skiltys, pati pirmoji skirta fazės moduliacijai bei aktyvuoti vidinį 6x daugiklį. Likusios 4 skiltys apibrėžia generuojamą dažnį. Taip suskaldytas registras gali būti užpildytas lygiagrečiai (3 pav.). Kaip matyti paveiksle pradžioje „numetamas“ (RST) 40 bitų registras. Po to seka 5 ciklai (WCLK), tai lygiagretus duomenų (DATA) surašymas į AD9851. Surašius duomenis iš karto išėjimo virpesio dažnis nepasikeičia, tą vykdo FQ_UD. Minusas šios mikroschemos yra tai, kad norint pakeisti sintezatoriaus dažnį, reikia perrašyti visą 40 bitų registrą. Bet įvertinant tai, kad mikrovaldikliai gali dirbti didele sparta tai, trūkumas lengvai apeinamas.

3 pav. Sintezatoriaus valdymo laiko diagramos

4 paveiksle pateikta „Atmega 16“ jungimo schema prie AD9851, likusioji dalis yra standartinė. Maitinimas AD9851 reikalingas atskiras, joje išskirta analoginė bei skaitmeninė dalis. Blogiausiu atveju abi maitinimo grandines galima sujungti ir padaryti bendrą su „Atmega 16“. 100 K varža gali būti pakeista 50 K ar 25 K, tiesiog ja keičiama įtampos reikšmė, kuri per sintezatorių keičiama į generuojamą dažnį. Taip gauname paprastą dažnio valdymą, tik reikt turėt omenyje, kad programos pavyzdys rašytas vidinei „Atmega“ atraminei 2,5 V įtampai ir kad maitinimo įtampos svyravimas turės įtakos generuojamam dažniui. Tokiam efektui sumažinti, galite naudoti gerai stabilizuotą maitinimo įtampą. Kondensatorius jungtas prie kintamos varžos sumažina staigių įtampų šuolių įtaką ir reguliavimas gaunasi pakankamai stabilus.

4 pav. AD9851 jungimo prie „Atmega 16“ schema

AD9851 veikimui pademonstruoti, sudarysim programą skirtą populiariam FM diapazono virpesiams generuoti, kadangi lengva bet kokiu radijo imtuvu patikrinti be oscilografo ar veikia pagamintas prietaisas. Kaip žinoma, FM radijo stočių moduliacijos plotis užima 50 kHz (Mono kanalas 25 kHz o likusi dalis stereo signalo pernešimui). Stereo realizaciją galima padaryti programiškai, bet paprastumo sumetimais programa pateikta MONO atvejui. Bandymams AD9851 generatoriui panaudotas 23,4 MHz kvarcinis rezonatorius, kuris per vidinį mikroschemos daugiklį padaromas 6 kartus didesnis 140,4 MHz (P. S. Maksimalus rezonatorius gali būti 30 MHz). Sintezatoriaus generavimo dažnio priklausomybę galima nustatyti pagal tokią formulę:

Čia fsist – AD9851 vidinis taktinis dažnis, mūsų atveju 6x23,4= 140,4. R – registro reikšmė – skaičius apibrėžiantis sintezatoriaus dažnį.

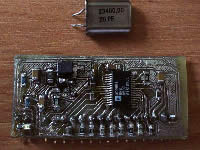

Apie detales ir konstrukciją

Bandymams naudojau SMD elementus, kadangi dažnio sintezatorius yra planarinis, be to tokia konstrukcija užima daug mažiau vietos. Schemos PCB (Autocad DWG formate) skirtą optiniam ar kitokiam plokštės padarymui galite parsisiųsti čia: dds.dwg.

10 K Rx varžų galima nenaudoti, bet juos įdėjau saugumo, statinio lauko atveju, sumetimais. Vedančiajam generatoriui panaudotas SMD tranzistorius BC817-40 (Q1), bei SMD droselis 200–300 uH. Šiuo atveju gali tekti paderinti emiterio grandinėje esančią varžą, kad generatoriaus išėjime gautųsi kuo artimesnis sinusui virpesys. Jei generatorius nesusižadina, galima R3 rezistoriui lygiagrečiai prijungti 0,1 nF kondensatorių. Schemoje vietoj 10 uF panaudoti 4,7 uF SMD nepoliariniai kondensatoriai. Labai jau didelės reikšmės jų talpa neturi, jei gerai stabilizuotas maitinimo šaltinis, bet jų naudojimas yra būtinas, kadangi schema gali generuoti pakankamai aukštus dažnius. Varža R5 skirta SAK išėjimo srovės reguliavimui ir neturėtų būti mažesnė nei 2 K. Bandymų metu pastebėtas jautrumas maitinimo įtampai, patartina nemaitinti schemos didesne nei 5 V įtampa. Taip pat mikroschema kaista, bet papildomo aušinimo nereikia. Nerekomenduoju šuntuoti išėjimo, geriausia nemažinti R6 varžos reikšmės. Nesant žemų dažnių filtro, su nukirtimo dažniu 80–70 MHz oscilografe, o geriau spektro analizatoriuje galima matyti sintezatoriaus papildomas aukštesnes harmonikas. Programos kodas skirtas FM dažnio ruože sintezavimui, pateiktas žemiau.

#include <iom16.h>

#include "ina90.h"

// Laiko vėlinimo funkcijos deklaravimas

void Laikas2(unsigned int m);

unsigned char *w, v=0; // Kintamųjų apibrėžimas

long p=0x000000;

// Nustatome 31,99 MHz dažnį prie

// 23,4 MHz kvarcinio rezonatoriaus

long fm_daznis=978909925;

// max skaicius 1694106900

void main(){

DDRD=255;

DDRA=7; DDRC=255;

DDRB=255;

//Reset sintezatoriui įvykdymas (RST)

PORTA=4;

Laikas2(200);

PORTA=0;

// Nustatome multiplekserį (37 išvadas „Atmega 16“)

// bei analogas-skaičius keitiklį į veikimo padėtis

ADMUX=(1<<REFS1)|(1<<REFS0)|(0<<ADLAR)|(0<<MUX4)|

(0<<MUX3)|(0<<MUX2)|(1<<MUX1)|(1<<MUX0);

ADCSRA=(1<<ADEN)|(1<<ADSC)|(1<<ADFR)|(1<<ADIE)|

(1<<ADFR)|(1<<ADPS2)|(1<<ADPS1)|(1<<ADPS0);

_SEI(); // Įjungiamos globalios pertrauktys

while(1)

{}

}

// Analogas-skaičius keitiklio funkcija

#pragma vector=ADC_vect

__interrupt void Analog()

{

long a=0, b=0; char i; // Vidinių kintamųjų apibrėžimas

Laikas2(20);// Vėlinimo laikas moduliacijos dažniui keisti

a=ADC; // Nuskaitome skaitmeninę įtampos reikšmę

PORTB=a;// Atvaizduojame įtampos reikšmes šviesos dioduose

a*=298739; // Dažnio keitimo diapazono reguliatorius

// Įjungiame vidinį 6x dažnio daugiklį

PORTC=1;

PORTA=1;

PORTA=0;

// Paprastos 50 KHz deviacijos realizacija

if (v==0){

// Skaičius 1529547 apibrėžia 50 KHz deviaciją

b=1529547; v=1;

}

else{v=0;b=0;}

p=fm_daznis+a+b; // Virpesio dažnio formavimo kintamasis

// Suskaidome p kintamąjį po 8 bitus siuntimui

w = (unsigned char*)&p;

// 8 bitų paketų siuntimo ciklas (DATA),

// skirtas užpildyti vidinį dažnio nustatymo registrą

for (i=0; i<4; i++)

{

PORTC=w[3-i];

PORTA=1;// WCLK formavimas

PORTA=0;

}

PORTC=0;

//Duomenų galiojimo patvirtinimas FQ_UD

PORTA=2;

Laikas2(2);

PORTA=0;

}

// Laiko vėlinimo funkcija

void Laikas2(unsigned int m)

{

unsigned int i=0;

for (i=0; i<m; i++)

{}

}

Sukompiliuotą, testavimui skirtą programėle galite parsisiųsti čia: test.hex

Štai keletas paveiksliukų, iliustruojančių sukonstruotą ir gerai veikiantį modelį:

|

|