Jei lanksčios integrinės schemos būtų prieinamos jau šiandien, elektroninių produktų gamintojai galėtų nudžiuginti neįprastais ir iš tikrųjų lanksčiais įrenginiais. Ir štai galiausiai mokslininkams iš Ostine esančio Teksaso universiteto (JAV) pavyko sukurti metodą, kuris leidžia gauti didelio produktyvumo lanksčias integrines schemas, o tam buvo panaudota standartinė įranga bei medžiagos, kurios naudojamos tradicinių mikroschemų gamyboje.

Jei lanksčios integrinės schemos būtų prieinamos jau šiandien, elektroninių produktų gamintojai galėtų nudžiuginti neįprastais ir iš tikrųjų lanksčiais įrenginiais. Ir štai galiausiai mokslininkams iš Ostine esančio Teksaso universiteto (JAV) pavyko sukurti metodą, kuris leidžia gauti didelio produktyvumo lanksčias integrines schemas, o tam buvo panaudota standartinė įranga bei medžiagos, kurios naudojamos tradicinių mikroschemų gamyboje.

Iš pradžių tam, kad sukurtų lanksčias schemas, mokslininkai dažnai griebdavosi visiškai naujų puslaidininkių gamybai medžiagų, tokių kaip puslaidininkiniai polimerai arba neorganiniai nanolaidai. Kitos mokslininkų grupės bandė laimę su tradiciniu polikristaliniu siliciu, arba tiesiog užpurkšdami įvairias silicio formas ant plastikinių plokštelių. Nežiūrint į tai, kad kai kurie metodai tam tikra prasme būdavo sėkmingi, visa tai reikalavo atsisakyti šiuolaikinės (puikiai veikiančios, tačiau gana brangios) įrangos.

Savo ruožtu, mokslininkai iš Teksaso universiteto pasiūlė bet kokio sudėtingumo integrinių schemų gamybos metodą, kuris nereikalauja kažkokių ypatingų pakeitimų dabartiniuose technologiniuose procesuose, o tai leidžia tikėtis šio metodo greito įdiegimo.

Mokslininkai pabandė surasti patogų būdą, kuris leistų supjaustyti paprastas silicio plokšteles („wafer“) į dar smulkesnius lapelius, kurie dėl savo plonumo tampa lankstūs. Taigi iš pradžių pasiūlyti norimos integrinės schemos „vaizdą nupiešti“ ant standartinės 200 mm silicio plokštelės, naudojant „senas“ gamybines linijas. Tokių plokštelių storis – apie 600–700 mikrometrų, tuo tarpu silicis lankstus tampa, kai storis sudaro maždaug kelias dešimtis mikronų. Būtent tokį sluoksnį su jau „nupieštu“ schema ir reikia atskirti nuo likusios plokštelės.

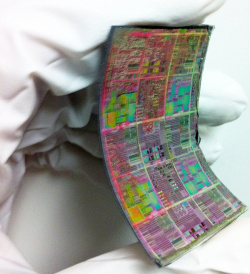

Visa tai padaryti pavyko gana originaliu būdu. Silicio plokštelę su nupiešta integrine schema galvaniniu būdu padengė plonu 50–100 mikrometrų storio nikelio sluoksniu. Vėliau gautą metalizuotą plokštelę pašildė iki 100˚C. Šildant silicis ir nikelis plečiasi skirtingu greičiu, o tai sukelia savotišką stresą, kuris veikia silicį. Tokiu būdu plokštelės kraštuose, maždaug 20–30 mikrometrų nuo plačiosios plokštumos, įvyksta lūžis (padeda integralinės schemos „paveikslas“, kuris sumažino medžiagos pasipriešinimą viršutiniuose sluoksniuose). Naudojant labai ploną laidą, lūžis paspartinamas per visą plokštumą. Visą procesą galima palyginti su labai plonų sūrio griežinėlių pjaustymu. Po to, kai nikelis pašalinamas (galbūt naudojamas kažkoks rūgštinis tirpalas), gaunamas plonas ir lankstus silicio lapas su iš anksto padarytu integralinės schemos „paveikslu“.

Įdomu tai, jog ši technologija gana greitai buvo teigiamai įvertinta puslaidininkių mikroschemų gamintojų. Štai kompanija SVTC (JAV) šį metodą jau spėjo panaudoti daugiasluoksnių trimačių mikroschemų gamyboje (priminsime, kad tai leidžia gauti didesnį produktyvumo lygį mažesniame kristalo plote). Tokiu būdu, galima tikėtis, kad greitu metu pamatysime tikrai lanksčius įrenginius. Juk turime ne tik lanksčius ekranus, tačiau ir lanksčias baterijas, o čia dar silicio mikroschemos pakeliui…