Mokslininkai iš Singapūro Mokslų, technologijų ir tyrimų agentūros (A*STAR) sukūrė naują 3D puslaidininkių komponavimo metodiką, kuri leidžia sumažinti plotą, užimamą dviejų tranzistorių, praneša resursas Phys.Org.

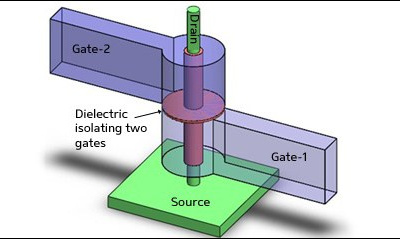

Mokslininkų pasiūlyta idėja paprasta: du tranzistorius vieną virš kito būtų galima patalpinti, pasinaudojus vertikaliu stulpeliu. Idėjos autoriai panaudojo taip pat vadinamas „apjuosiančias“ užtūras (wrap-around gates), kurie turi cilindrą su jo centre esančiu nanolaidininku. Tarp užtūrų izoliatoriaus vaidmenį atlieka dielektriko sluoksnis.

Mokslininkai jau pademonstravo, kaip galima sukurti paprasčiausią loginį elementą, kurio pagrindą sudaro vienas nanolaidininkas ir du vertikaliai išdėstyti tranzistoriai. Pasiūlytoje schemoje elektros srovė prateka tuo atveju, jei įtampa abiejose užtūrose yra aukšta. Esant žemai įtampai, elektros srovė neprateka.

Dėl to, jog tranzistoriai patalpinami vertikaliai, jų užimamas plotas sumažėja dvigubai. Perspektyvoje pasiūlyta Singapūro mokslininkų metodika gali būti panaudota elektroninėse schemose su 3D struktūra.