Tam, kad tyrėjai galėtų kurti išmanesnius, mažesnius ir galingesnius elektronikos įrenginius, reikia atsižvelgti į tranzistorių grandinių – pagrindinių tokių įrenginių sudedamųjų dalių – pajėgumus apdoroti didžiulius informacijos kiekius. Šioms grandinėms nepaliaujamai spartėjant ir mažėjant, jose pasitaikančių apdorojamos informacijos klaidų skaičius, kurį lemia šilumos sklaida, triukšmai ir sandaros netvarka, gali apsunkinti tolimesnę technologijų raidą.

Ekspertai ginčijasi, bandydami sutarti, kuris iš dviejų klaidų mažinimo procesų yra veiksmingesnis ir našesnis, kuomet grandinių matmenys pasiekia nanomastelį: (1) leistinas fizinis klaidų nuokrypis, kai įrenginys yra mažinamas iki tokio dydžio (ir elektronų skaičiaus), kad jis vis dar pajėgtų veikti be loginių klaidų, arba (2) leistinas architektūrinis klaidų nuokrypis, kai įrenginys yra mažinamas neribotai, tačiau tuo pačiu metu taikomi sudėtingi daromų klaidų taisymo algoritmai.

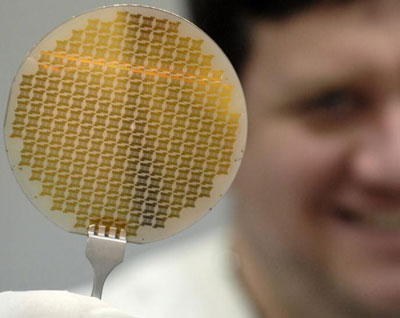

Naujausiame savo darbe elektros inžinerijos profesorius Vanis Roichovduris (Vwani Roychowdhury) iš Kalifornijos universiteto (JAV) kartu su elektros ir kompiuterių inžinerijos profesoriumi Tomasu Skopeku (Thomas Szkopek) iš Makgilo universiteto (Kanada) bei kitais kolegomis pirmąkart įvertino šiuos klaidų mažinimo procesus modelinėms nanoelektronikos sistemoms ir apskaičiavo minimalų elektronų skaičių, reikalingą, kad grandinė veiktų patikimai. Tyrėjai išsiaiškino, jog leistinas fizinis klaidų nuokrypio mechanizmas klaidų skaičių, tenkantį elektronui, tranzistorių grandinėse sumažina rodikliškai, kai tuo tarpu netgi pats efektyviausias architektūrinis klaidų taisymo mechanizmas nepasižymi rodikliniu rezultatu. Mokslininkai padarė išvadą, kad fizinis klaidų taisymo mechanizmas yra pranašesnis už architektūrinį klaidų taisymą.

Atliktas tyrimas reikšmingas tuo, kad suteikia įžvalgų, leidžiančių įvertinti nanomastelinių tranzistorių technologijų patikimumą ir įtaisų mažinimo galimybę, galbūt netgi apibrėžia minimalų galimą įrenginių dydį. Gauti rezultatai gali būti iškart taikomi tyrėjų, dirbančių tranzistorių mažinimo srityje, ir mokslininkų, kuriančių ateities prototipus.