AMD ISSCC 2020 renginio metu pasidalino keliomis skaidrėmis, kuriuose detalizuoja „Zen 2“ procesorių architektūros čipelių dizaino privalumus. Pagrindinė čipelių dizaino nauda yra galimybė projektuoti mažesnius lustus, o tokių lustų gamyba yra kur kas pigesnė nei vieno didelio monolitinio lusto. Be to, galima panaudoti senesnės litografijos lustą jungtims ir atminties valdikliui, o tai irgi sumažina bendrą procesoriaus pagaminimo kainą.

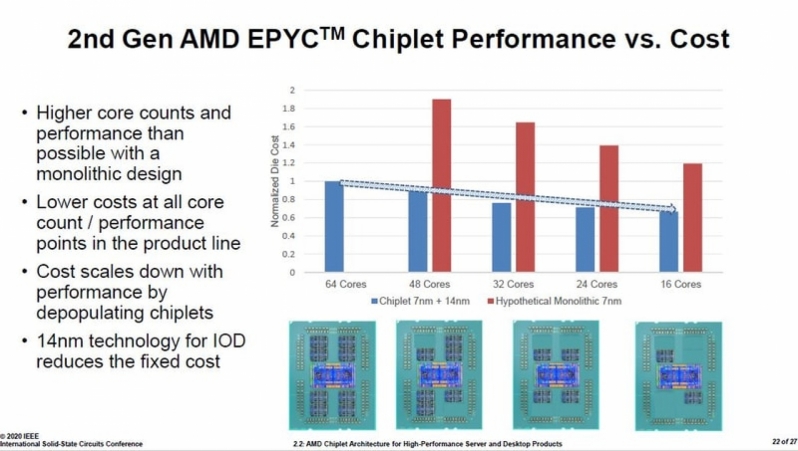

Pirmoje skaidrėje matome EPYC procesorių analizę. AMD sako, kad dabar 64 branduolių procesorius monolitiniame luste yra neįmanomas net su 7 nm litografija, todėl net nėra palyginimo kiek sutaupo čipelių dizainas. 48, 32 ir 24 branduolių procesorių gaminant monolitiniame luste AMD gamybos kaštai būtų maždaug du kartus didesni. 16 branduolių procesorius iš čipelių dizaino gauna mažiau naudos, bet ji vis tiek yra labai didelė. Tokios procesoriaus monolitinis lustas būtų maždaug 1,7 kartus brangesnis.

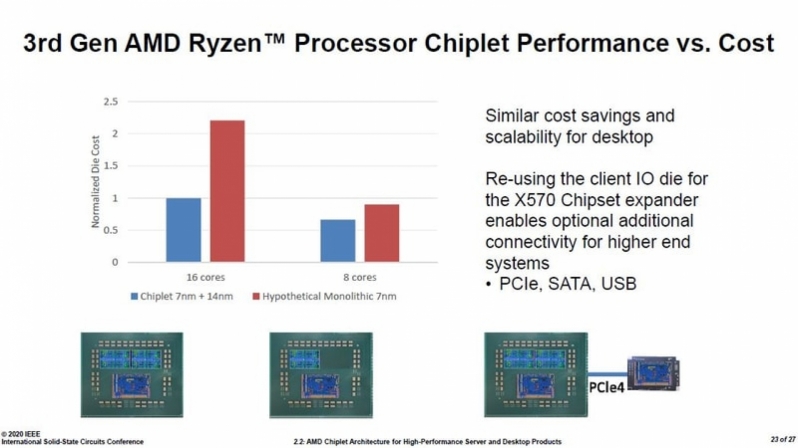

Kitoje skaidrėje jau „Ryzen“ procesoriai. AMD sako, kad 16 branduolių procesorius viename luste būtų daugiau nei du kartus brangesnis nei jį gaminant panaudojus čipeles. Dabar AMD norint išgauti „Ryzen 9 3950X“ procesorių panaudoja du 7 nm lustus su branduoliais ir vieną 14 nm lustą su atminties valdikliu ir visomis jungtims. Kalbant apie 8 branduolių procesorių nauda yra jau mažesnė, bet vis tiek yra.